SYSTEM C (CHƯƠNG I)

CHƯƠNG I: GIỚI THIỆU TỔNG QUAN VỀ THIẾT KẾ

HỆ THỐNG SỬ DỤNG SYSTEM C

1.1 Giới thiệu

System C là một ngôn ngữ thiết kế

hệ thống đã phát triển và đáp ứng nhu cầu phổ biến cho việc cải thiện tổng thể

năng suất của hệ thống điện tử cho những nhà thiết kế. Các hệ thống ngày nay chứa

các ứng dụng riêng cả về phần cứng lẫn phần mềm. Hơn nữa, phần cứng và phần mềm thường phát triển đồng thời

và có mối quan hệ chặt chẽ với nhau, các hệ thống đòi hỏi phải có mối ràng buộc

về hiệu suất thời gian thực chặt chẽ, kiểm tra chức năng kỹ lưỡng để tránh những

thất bại không mong muốn, thậm chí là không thể thực hiện.

System C mang lại những lợi ích

thiết thực bằng cách cho phép các kỹ sư thiết kế cả phần cứng và phần mềm vì cả

hai đều sẽ tồn tại ở sản phẩm cuối cùng. Mức trừu tượng cao giúp cho nhóm thiết

kế sớm hiểu cơ bản về một tiến trình thiết kế phức tạp và tương tác với toàn bộ

hệ thống để cải thiện, xác minh hệ thống tốt hơn và dễ dàng hơn. Trên hết đó là

lợi ích về năng suất thông qua việc tận dụng các mô hình hệ thống ban đầu hoặc

có sẵn để tiến hành thực thi một hệ thống theo yêu cầu.

1.2 So sánh ngôn ngữ

Nói chính xác thì system C không

phải là một ngôn ngữ mà là một lớp thư viện trong một ngôn ngữ được thiết lập tốt

như C++. System C không phải là tốt nhất nhưng nó sẽ giải quyết các vấn đề về

năng suất thiết kế. Tuy nhiên, khi

System C đi chung với thư viện System C Verification nó cung cấp một ngôn ngữ

có nhiều đặc điểm liên quan đến thiết kế hệ thống và mô hình hóa các tác vụ còn

thiếu hoặc phân tán giữa các ngôn ngữ khác. Ngoài ra, System C còn cung cấp một

ngôn ngữ chung cho cả phần cứng lẫn phần mềm.

Một số ngôn ngữ đã hình thành để

giải quyết các khía cạnh khác nhau của thiết kế hệ thống. Mặc dù Ada và Java đã

chứng mình được giá trị của bản thân, C/C++ được sử dụng chủ yếu hiện nay cho

các phần mềm hệ thống nhúng. Ngôn ngữ mô tả phần cứng(HDLs), VHDL và Verilog,

được sử dụng để mô phỏng và tổng hợp các mạch kỹ thuật số. Vera và e là các

ngôn ngữ được lựa chọn để xác minh chức năng của các mạnh tích hợp có ứng dụng

phức tạp (ASIC). SystemVerilog là một ngôn ngữ mới phát triển từ ngôn ngữ

Verilog để giải quyết nhiều vấn đề thiết kế hệ thống theo định hướng phần cứng.

Matlab và một số công cụ, ngôn ngữ khác như SPW và System Studio được sử dụng rộng

rãi để thu thập các yêu cầu hệ thống và phát triển các thuật toán xửa lý tín hiệu.

1.3 Phương pháp thiết kế

Các phương pháp thiết kế sử dụng

System C hiện đang phát triển và có sự thay đổi rộng rãi. Trong một vài năm tới,

các phương pháp sẽ có khả năng thống nhất thành một phương pháp gắn kết ( với một

vài biến giá trị trong phân đoạn ngành). Kết quả của các phương pháp sẽ cảm thấy

tương tự như các phương pháp được sử dụng ngày nay, nhưng ở mức trừu tượng cao

hơn. Đối với một số người khái niệm phát triển phần cứng và phần mềm trên cùng

một ngôn ngữ là một cuộc cách mạng lớn, nhưng đây là con đường phát triển cho

những người làm việc trong cả hai lĩnh vực.

Mặc dù các công cụ và cấu trúc

ngôn ngữ tồn tại trong SystemC để hỗ trợ tổng hợp và mô hình hóa RTL ( Register

_ tranfer _ level ), một lý do chính để sử dụng ngôn ngữ là làm việc ở mức trừu

tượng cao hơn cả RTL. Khả năng mô hình hóa thiết kế RTL của systemC cho phép hỗ

trợ các khối thiết kế được tạo ra bởi các công cụ tổng hợp cấp cao (hành vi hoặc

đồ họa) hoặc để hỗ trợ các khối thiết kế kế thừa.

1.4 Nâng cao năng suất với System C

SystemC sử dụng để đạt được yêu cầu

và nâng cao năng suất để thiết kế hệ thống điện tử ngày càng phức tạp. Nếu

không chú ý tăng năng suất thì nhiều khái niệm hệ thống mới sẽ không thực tế.

1.4.1

Tăng độ

phức tạp của thiết kế

Hệ thống điện

tử hiện đại bao gồm nhiều hệ thống phụ và các thành phần nhưng chúng ta sẽ tập

trung chủ yếu vào phần cứng, phần mềm và thuật toán. Trong các hệ thống hiện đại

mỗi ngành đều trở nên phức tạp hơn. Tương tự như sự tương tác ngày càng phức tạp.

Ngụ ý của

“tương tác” ở đây là việc trao đổi của các vùng trở nên quan trọng để đáp ứng

yêu cầu của khách hàng. Các câu hỏi được đặt ra cho người thiết kế “Chức năng

này có nên thực hiện trong phần cứng hay phần mềm hay thuật toán sẽ tốt hơn”? Hệ

thống rất phức tạp chỉ cần mấy thông số kỹ thuật từ yêu cầu của khách hàng đã

trở thành một nhiệm vụ khó khăn.

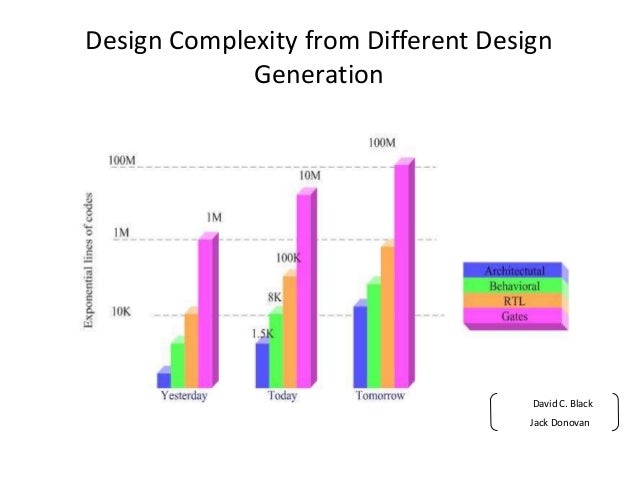

Hình dưới đây

sẽ minh họa các vấn đề phức tạp khi thiết kế phần cứng cho một hệ thống trên

thiết kế chip (SoC).Thông số này cho thấy mẫu thiết kế từ 3 thế hệ.

·

Architecture

·

Behavioral

·

RTL

· Gates

· Gates

Các mạch tích

hợp ngay nay (IC) thường vượt qua quá 10 triệu cổng, trong đó có thể dịch thành

một trăm nghìn mã RTL. Các thiết kế ngày nay là thiết thực vì các phương pháp

áp dụng tổng hợp RTL để tạo ra các cổng tự động. Tương lai IC sẽ vượt quá một trăm triệu cổng hoặc khoảng một triệu dòng mã RTL nếu được viết bằng các phương

pháp của hiện tại.

Lưu ý rằng

hình trên chỉ xem xét một mạch tích hợp duy nhất. Nó không phản ánh độ phức tạp

của một hế thống chip lớn như ASIC và FPGA hoặc ứng dụng phần mềm của gigabyte.

1.4.2

Đối mặt

với thiết kế phức tạp

SystemC hỗ trợ

một số kỹ thuật để giải quyết sự phức tạp của thiết kế hiện đại. Thiết kế ngày

nay mọi người thường sử dụng một số phương pháp để giải quyết các vấn đề phức tạp

đi kèm với hệ thống phức tạp:

·

Abstraction ( Sự trừu tượng)

·

Design reuse (Kế thừa thiết kế)

·

Team discipline (Kỷ luật nhóm)

·

Project reuse ( Tái sử dụng dự án )

·

Automation ( Tự động hóa )

1.4.2.1

Abstraction

Trong quá khứ, kỹ

thuật chính để quản lý sự phức tạp cho cả cộng đồng phần cứng và phần mềm là

nâng cao mức độ trừ tượng được sử dụng trong thiết kế. Cách tiếp cận này sẽ là

kỹ thuật chính trong tương lai.

Đối với các nhà

phát triển phần mềm, quá trình chuyển đổi từ mã assemble thành các ngôn ngữ cao

hơn như FORTAN và PL/I, sau đó là các

ngôn ngữ trừu tượng hơn như Lisp, Ada và các ngôn ngữ đa mô hình như C++. Các học

viên phần mềm ngày nay vật lộn với nhiều ngôn ngữ, khi họ cố gắng tìm mức độ trừu

tượng, tính linh hoạt và hiệu suất cần thiết để phát triển – duy trì các hệ thống

hiện đại. Lập trình mô đun, các biến dữ liệu, lập trình hướng đối tượng, lập

trình chung, xử lý ngoại lệ và xử lý ràng buộc

tất cả nhằm quản lý sự phức tạp.

Đối với cộng đồng

phần cứng, thiết kế cấp độ cổng đã kết nối thông qua các công cụ sơ đồ ảnh và

ngôn ngữ cấp độ cổng xuất hiện rất thô sơ theo các tiêu chuẩn ngày nay. Vào cuối năm

1980, VHDL và Verilog đã cho phép mô phỏng ASIC, tài liệu và phát triển

net list, cuối cùng là tổng hợp RTL.

Thật không may,

tổng hợp RTL cả VHDL và Verilog để xác minh hành vi trên mỗi cạch xung clock,

cung cấp ít mức trừu tượng hơn mà C đã cung cấp cho các nhà thiết kế phần mềm. Trong

khi phần mềm thiết kế như C++ đã tăng tốc trong thập niên 1990 cụ thể là thiết

kế phần mềm hướng đối tượng, các nhà cung cấp EDA đã cố gắng bắt kịp bằng cách

cung cấp các công cụ tổng hợp hành vi có thể xây dựng từ các mô tả VHDL và

Verilog trừu tượng hơn. Các nhà cung cấp EDA tập trung vào việc tái sử dụng thiết

kế và đáp ứng các yêu cầu về năng suất thiết kế.

Kết quả là, cộng

đồng phần cứng đã không đưa ra mức trừu tượng vượt quá RTL trong gần 20 năm và

cộng đồng thay vào đó là việc kế thừa thiết kế, kỹ luật nhóm và tự động hóa.

1.4.2.2

Design

Reuse

Việc tái sử dụng

hay kế thừa đã gần như thống trị cả trong kỹ thuật-năng suất cho RTL lẫn thiết

kế phần mềm. Nhiều tài liệu đã viết về chủ đề này, việc kế thừa sẽ tiếp tục là

một phần quan trọng của bất kì phương pháp mới nào để góp phần giải quyết sự phức

tạp ngày càng tăng.

Thiết kế dựa

trên nền tảng là một sự phát triển của việc thừa hưởng thiết kế và phát triển nó đến mức trừu tượng

cao hơn. Thay vì sử dụng lại các mức thiết kế thấp hơn, toàn bộ nền tảng tính

toán hiện nay được tái sử dụng và được lập trình cho các ứng dụng cụ thể.

1.4.2.3 Team discipline

Team

discipline đề cập đến các công cụ và kỹ

thuật được sử dụng để mang lại năng suất cho từng kỹ sư và các tương tác giữa

các chuyên gia. Việc này bao gồm bất cứ điều gì từ kiểm soát sửa đổi các thông

số kỹ thuật tới các tài liệu để thiết kế và đánh giá code.

Trong quá khứ

thì Team Discipline đã được áp dụng ở cục bộ nhưng không phối hợp với các nhóm

kiến trúc, phần mềm và phần cứng.

Hơn nữa , Team

discipline đã được áp dụng nhưng không đồng đều và chặc chẽ ở mỗi nhóm. Để giải

quyết các vấn đề phức tạp ở các thiết kế, thế hệ tiếp theo cần phải áp dụng đồng

bộ hơn cho tất cả các quy tắc thiết kế hệ thóng, phối hơn chặc chẽ hơn.

Mô

hình tăng trưởng năng lưc (CMM) của Viện Công Nghệ Phần Mềm (SEI) đã góp phần đóng góp nhiều vào việc nâng cao quy

trình phát triển phần mềm từ kỹ thuật đến khoa học. Cộng đồng phần cứng đã chấp nhận

khái niệm MORE (Measure of Reuse Excellence).

1.4.2.4

Project

Reuse

Tái sử dụng dự

án là một thuật ngữ đề cập tới việc code của một dự án đã hoàn thành được tái sử

dụng lại ở một dự án tiếp theo. Các kỹ sư có thể thừa hưởng lại mã code của các

dự án ban đầu và tinh chỉnh lại.

1.4.2.5

Automation

Một phương pháp

quan trọng khác để giải quyết sự phức tạp của thiết kế là tự động hóa quá trình

thiết kế. EDA đã và đang liên tục cung cấp các công cụ cải thiện năng suất thiết

kế.

Hầu hết các công

cụ EDA đều đi kèm với các hướng dẫn mã hóa để tối đa hiệu suất công cụ và năng

suất của kỹ sư. Đặc biệt với số lượng RTL tăng theo cấp số nhân cần thiết cho một

hệ thống hiện đại. Kỹ thuật Team discipline đi một chặng đường dài hướng tới việc

tận dụng tối ưu các công cụ mà EDA sử dụng.

Ngoài việc tạo

code tự động, tự động viết bởi nhóm phát triển luôn luôn cần thiết và có tầm

quan trọng hàng đầu đối với các luồng thiết kế hệ thống.

Post a Comment: